To this end you can use the CPLD Fun Board I made for this purpose, or another business card containing a EPM240T100 CPLD or another of the same family. Of course, first of all you need a card “development” which contains a CPLD EPM240T100. Hours we will see that “ingredients” They need to start using the CPLD EPM240T100 representing “entry level” Max II family. The CPLD programming is to load the configuration (also known as bitstream) within the EEPROM and CFM, if used, within the FOM. Within a EPM240T100 type CPLD we're going to use are 240 The, in addition there is an EEPROM memory block that holds the configuration to be loaded at power (CFM), and a further user EEPROM memory block (UFM). The Flip-Flop constitutes an atomic memory element which can be associated with the logical function of the LUT (to realize, and example, logs, counters, etc.). The LUT can be regarded as a kind of “PROM decoding”, programming it is possible to realize a logic function at will within the LUT. Wanting to simplify, an LE is constituted by a LUT (Look Up Table) with 4 inputs and by a Flip-Flop.

In the case of the family of Max II of Altera devices (now Intel), the atomic element is called LE (Logic Element) and it differs from the classical macrocella the GAL (product of terms such as AND-OR): The fundamental element of the CPLD is the macrocella, which constitutes the atomic logic element.

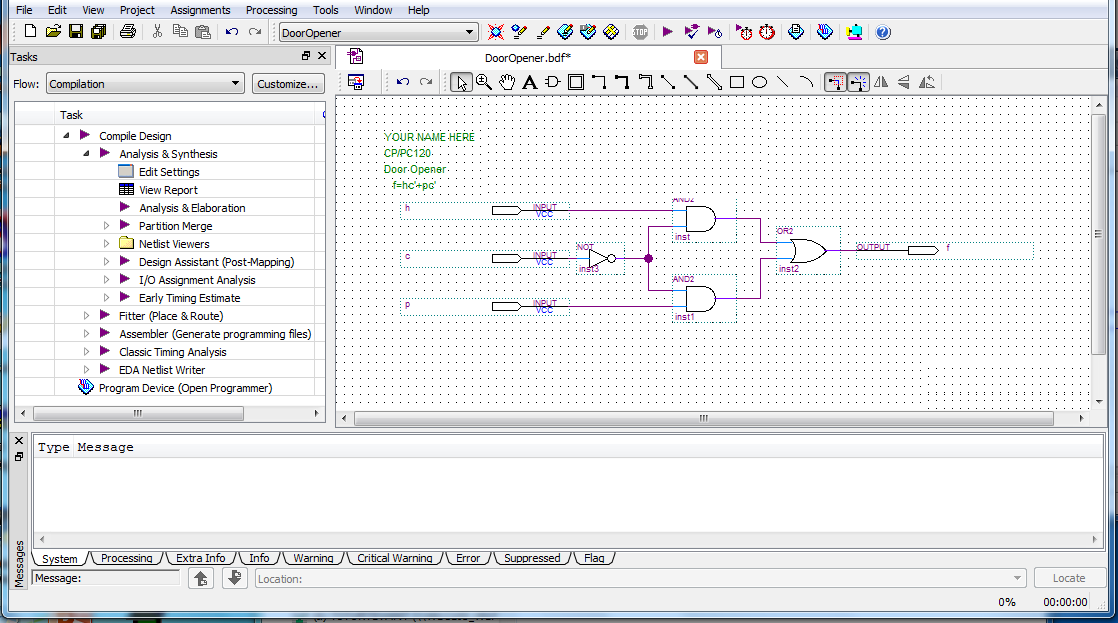

A further evolution of the CPLD is represented by FPGA (for more information see who) much more powerful and complex than CPLD, and they typically require an external memory for storing the configuration. It is an evolution of prior programmable logic devices such as PAL and GAL (for more information see who). I can't say it isn't synthesisable though, just looks weird to me.A CPLD (Complex Programmable Logic Device) It is a digital device that allows to program the logic functions to be implemented within the same device.

#Altera quartus ii connecting wire to input code

While all VHDL code can be simulated, only a subset can be converted into gates (synthesised).

#Altera quartus ii connecting wire to input full

Porting of legacy code to modern compilers generally requires a firm grasp of the language, so you might want to start by reading this reference guide to find out more about types and packages.Įdit: Are you sure this code is even synthesisable? Do you know if it has been used before to program a device? Its full of for/while loops and wait statements, which can make synthesis tricky. I can't guarantee his will entirely fix it, but will get you started. Replace "MVL7" and "clk" in your code with "std_logic", and " MVL7_Vector" with std_logic_vector. The type "clk" appears to be custom as well, and should also be replaced with std_logic.Īny remotely modern VHDL tutorial will show you the syntax, but in short remove the use statements at the top of 8251.vhdl and replace with library ieee You probably don't want to be using that with your Xilinix toolchain, as I doubt it will synthesise, so instead use the VHDL standard std_logic to catch up to this century.

The file types.vhdl contains definitions for the type MVL7 which appears to be Synopsys specific. Your compiler needs all of the input files to work, not just 8251.vhdl, so adding types.vhdl to your project would seem to be a solution at first, but I wouldn't recommend you do that. That error message is the compiler complaining that it cannot find the package types (defined in types.vhdl) in your local project, which is known as "work" for short.

0 kommentar(er)

0 kommentar(er)